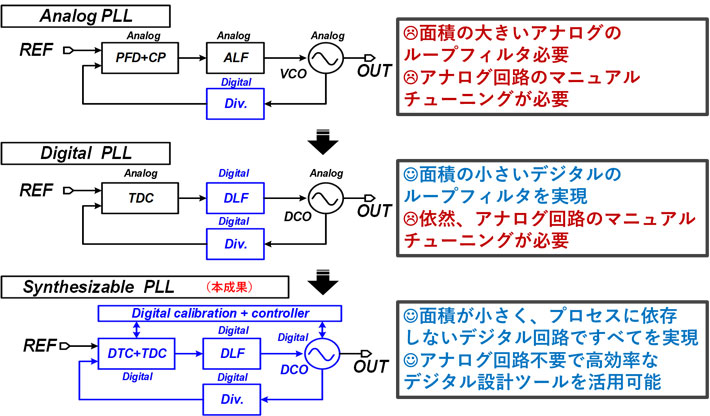

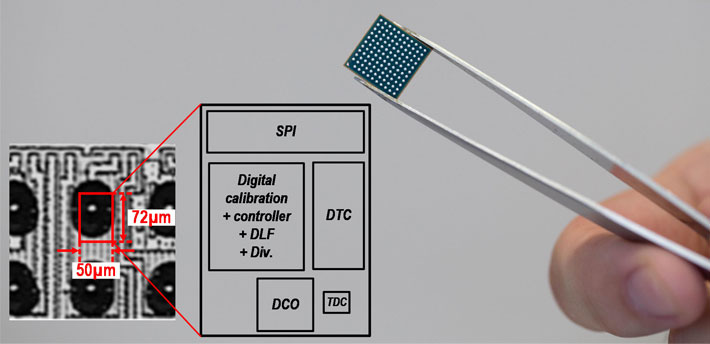

クロック回路はプロセッサーやメモリーといった半導体の各機能の間で同期を取るために使う。通常はアナログ回路で構成されるため、専門技術者の調整が必要だった。ソシオネクストなどはデジタル回路で構成することで、調整の手間を省きながら、回路面積は0.0036平方ミリメートルに抑えた。デジタル回路で一般的な自動設計も適用できる。

ソシオネクストと東工大は今後も、関連分野の基礎技術開発で協力していくという。

(専門知識をお持ちの方向けに東工大プレスリリースを置いときます)

世界最小のクロック回路を5 nm CMOSで開発 | 東工大ニュース | 東京工業大学

https://www.titech.ac.jp/news/2020/046252.html

2020/2/12 13:19

日本経済新聞

https://www.nikkei.com/article/DGXMZO55510200S0A210C2X20000/