2000年 デュアルコアPOWER4

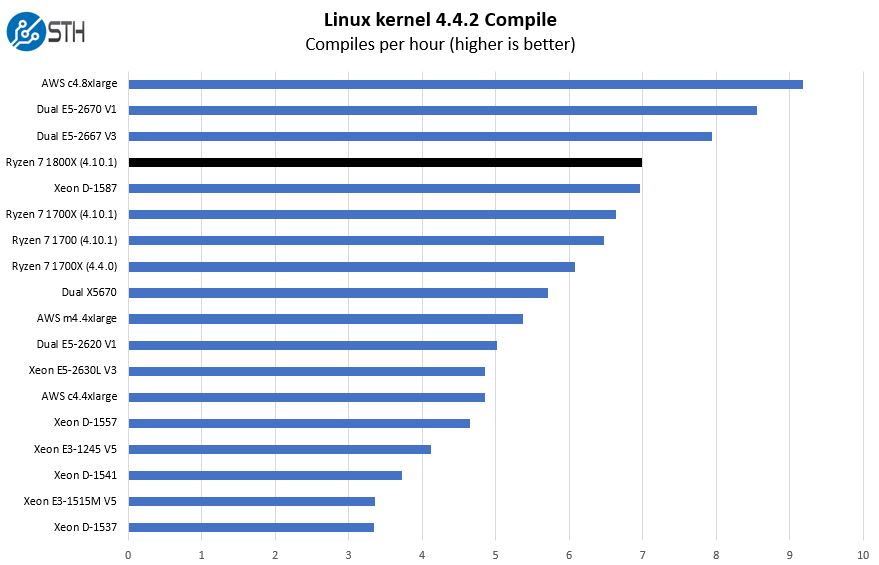

PassMarkとCPU-Zについてはフェイクの可能性が指摘されていますね

シングルスレッド同クロックでRyzenとKaby Lake比較されたら インテルファンボーイ最後の拠り所IPCすら奪われ憤死

4亀がどんなIntelアクロバットベンチ養護やるかに注目だな

実ゲームでもRyzen圧勝だな VIDEO 4亀は今回はAMD擁護側に付いてる

>>15 Ryzenにすら値下げくらいしか対抗手段がないなら、Vega統合らしいRavenRidgeが出たらどうするんだろうか

>>17 >>18 >>17 >>17 >>20 >>23 FX-4300(8000円)+384SP=6800K(税抜き18000円)

APUはそう高くせんだろ

>>19 AMDは10年に1回位頑張るんだけど、Intelを刺激するだけで後が続かないんだよなぁ

>>30 あのさぁキャッシュメモリーのサイズがそれぞれ違うだろ >>34 L2を入れるか入れないかくらい統一しては >>26 >>38 シングルスレッド同クロックでRyzenとKaby Lake比較されたら なお、Intelはかなり追い詰められつつあり、原因の一端として「人工知能の隆盛はさまざまなチップの市場を作り出しており、 http://gigazine.net/news/20170227-intel-skylake-x-12core/ ギガジーンのシーゲート叩きは酷かった

ギガジーンはそこら辺のアフィまとめと同じだからURL貼るの規制して欲しいよ

私はなーんも分かってませんと告白する記事をわざわざ貼る奴の

>>42 コア数の部分は元記事がめちゃくちゃなんだが、

シーゲートの時も糞記事取ってきてディスってたからな

ギガジンってシェアに関わるくらい影響力が大きいのか?

人口知能分野でGPUがCPUを圧倒するとともに、NVIDIAがIntelを引き離すという恐るべき事態となっているのは事実。

瞬間値ではそりゃx86よりも開発サイクルが短いGPUが優位な立場になる

今年のvoltaとIBMのPOWER9にある程度流れるんだろうな

>>56 シリコン辺りのDeep learning性能が

普及の決め手はコスパだからなー。GPUの数の暴力はすさまじいものがある

8コアCPUにしてはアイドル電力が低いのもいいね。

nVidiaがfermiでGPGPUを強化する為に倍速にして爆熱失敗したのに似てる

>>61 >>59 >>68 >>69 >>70 >>72 Intelの本気は来年か再来年の新アーキテクチャまでお預けだね

ヒルズボロがNetburstみたいなとんでもない新アーキかP6みたいな20年も保つ礎を期待してる(PenM以降はP6+Netburstなんだが)

>>76 >>76 >>81 とりあえずRYZENは、インテルが舐めプ続けた時の保険にはなる

玄人やXeon使いやLinux使いほど

ZENコア世代のサーバー向けはIOをどうするのかな。デスクトップは

Unbuffered ECCメモリ使えるし、Xeon E3の領域にもRyzen進出できるチャンスあるかも

opteron出すにしてもxeonの半値以下にしないと売れない

>>73 自作もやってて趣味プログラマでコンパイラぶん回す勢は

LGA20xxは高い、デカイ、食う、ブート遅い、ってところをどーにかしてもらわないと

インテルが7700kと6900kの間のニッチ埋めないなら

>>67 インテルだけが突出する新型ベンチだらけになると予想

>>29 naplesの1ソケットあたり8チャネルのメモリコントローラが、

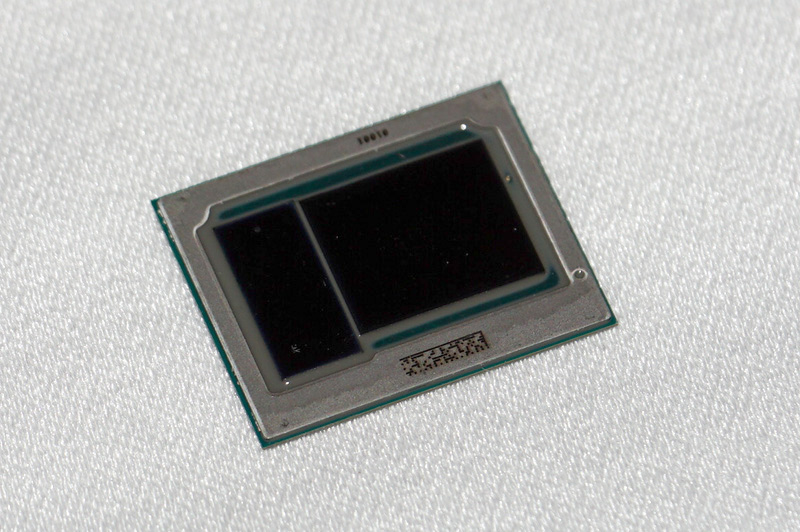

>>99 4チップMCM確定だぞ、普通にゴミじゃん

>>104 CPUタグを4〜5ビットに拡張してりゃノード内のスケーラビリティも十分問題ないが3ビットのままにしたせいで2ソケットで上限に達するというオチつけたからマザーボードの実装コスト上げただけのバカとしか言いようがないわな

ただしHPCへの投資も現時点で空振りネイティヴの32コアを作ったところで損益分岐点超えられるだけの見通しもないからそれが最適解なのだなというのは理解した

ネイティヴの2桁コアが作れないという点においてはもはやQualcommより下だな

理研の似鳥先生も4ch×4じゃダメなのか?てなことを言ってた

10年前のAMD広報の "Are youネイティヴ?" はもはや黒歴史かな

ラムバスあたりからFlexIOとかの高速シリアル通信のライセンスでも受けてピン数減らず努力してりゃ多少小さくまとまっただろうに

まあ、もう何を書こうとお笑いキャラなのは変わらないから、

そうそう、ゴミクズ糞団子の言うことなんて誰も信じないからw

それでLGA2011の倍以上のピン数引き出してマザーボード10層かそれ以上の高コストになったら世話ねーよ

16レーンが4つあるからそれぞれの2つ使って(更にいうなら2コア使って)アクセスしないとPCIe 32レーンのデバイスの性能を活かせない

4Pは今は手をつけないってだけだろうな

団子よく出てこれるなw

フォーカスというか、サーバ用の派生チップを細かく作る開発リソースがないのでは

Ryzen8コアはコスト的に絶妙なバランスだったな…

正直、8コアを本当に必要としてるユーザー、ほどんどいないと思うので

AMDのMCMって何があるの?

6コアのCoffee待ちの人は、Ryzenはどう思ってるんだろう

壊れなければ、Coffeeまで待つってのが多いだろう

>>119 >>125 Opteron >>125 CoffeeLakeは詳細のリークまだない気がするし、

65W枠の4コアに対して2コア足すと考えるなら無理なく6コア化できるかもね

インテルがigpu付き6コアに関してどうゆう用途を想定してるのか、謎だ

コーヒーは明らかにモバイル向け

ビデオ配信やVDI用のXeonE3の転用じゃないの?

>>128 >>138 ソケットあたり128レーンってえらく多いなと思ったら、

4つ組み込んでるRyzenのGPU用PCIe 16レーンを4系統とも外に引き出してるだけな。

>>140 >>142 64と16x4は全く意味が違うんだが知恵遅れにはわからんのだな

>>147 Southbridgeが無くなることで、コストダウンと省スペースと安定性が手に入るからね http://ascii.jp/elem/000/001/449/1449995/ 多コアでそれなりに高いTDPだとオンダイVRのメリットは大きいからもはや必須の技術だよね

>>149 CPUにLDOを搭載したことで、CPU毎、キャッシュ毎に電圧を細かく制御出来るようになり、

>>151 40レーンは1チップ・1ソケットあたり。

なんでIntelを語る時は「1ソケット40レーン!」で喜び、

AMD公式すらMCMと認めてるのにモノリシックだと勘違いして的外れな比較をするバカがいるから

8コア、DDR4 2ch、PCIe 16レーンの4人5脚が一人の巨人に見えてるバカが暴れてるの

XeonがMCMに頼ってた頃は全然スケールしなかったしIBMやCray案件もとれなかったからな

GPGPU専用カードであるRadeon InstinctとNaplesの相性はいいというアピール。

その構成は俺の主張となんら矛盾しないけど?それぞれのダイから16レーンを引き出すだけ。

NaplesからPCI-E 16レーンが4本出ているから、GPUを4つつけてもフル帯域でアクセス可能。

「VDI」は演算用じゃねーから

>>163 >>163-165 フルサイズでもないしフルスピードでもない

RyzenのCCX間とNaplesのそれが同じとは限らないってことか

あれ?

あぁ、Xeonの帯域を言わせた後に馬鹿にするつもりだったのにw

バカだねぇ

つーか複数ノードを繋いだ時の根元の帯域だろどうせ

Intel&CrayとIBM&NVIDIAが総取りしたプレゼンにも引っかからなかったしょぼスペックは欧米の研究機関はみんな知ってる

Naplesは上位Xeon相手に2倍以上の性能を示してるのに何を頓珍漢なことを話してるんだろう団子は

重箱の隅つつくようなベンチで勝った気になるいつもの手口で何行ってるんですか

帯域がボトルネックにならないSSE以下のFPのベンチを適当に選んでくればそりゃ勝てるでしょ

機械翻訳が2回線使って暴れてるのが手に取るように見えるのにわざわざ釣られにきてるスレがここですよ

今度は統失発症しててワロタ

団子は間違いを認めないからなー。大局で自論を主張すれば良いのに細部にこだわり過ぎ

Purleyで使えるPCI-Eは、

性能は十分に魅力あるものが設計できたようだが、

もうZENから立場が逆転してるんだよw >>188 あー、>188は瑕疵の期待や嫌味のように受け取ることもできるのか。

2ソケットあたり128レーンって情報は去年時点でも把握してたし「アクセラレータの母艦としてはいいんじゃない?」って言ってたと思うがな

前から出資はしてる

AMDがリーダーシップ取ってやってるCCIX、Gen-Z、OpenCAPIこのあたり全て調べてから書き込めよ

末尾r、わざわざワッチョイ出るスレで暴れなくても良いのに

PCはもう下火だし、タブレットは死んでるし、スマホもiphone以外うれねぇし

>>197 >>197 あと車載にはかなり前から技術投資してたりする

パソコンレベルの電力側からスライドの、大規模、複雑なCPU、GPUを

ニューラルネットの学習をするのと、学習結果を使って物体認識とかするの間では必要なリソースに大きな差がある

>>204 ぶっちゃけ自動運転とか生きてる間に実現する気が全くしないな

特に日本では難しいだろうね

子供や猫の急な飛び出しに安全に対応できるのが最低条件だな

まあ今の車も半分自動運転みたいなもんだしね

自動化は高速限定、一般道はカーナビと自動ブレーキとかが現実的かな

>>208 犬、猫、通行人、運転手、対向車

>>169 なんで顔真っ赤にして、CPUの外にあるomni-path fabricを力説してるんだろう

>>85 >>214 それ言うと100Gbitだと1本で12GB/秒だね

雰囲気づくりのみの中身の無いレス書かれても、また話について行けないアム厨かとしか感想出ない

ってかzenでサーバー云々のまえに企業信用どうにかしないと使ってもらえない現実

Cannonlake-EP/EXでPCIe 4.0に対応するだろうと言われてるがAMDはプラットフォームの刷新がほぼメモリの世代単位になるので大口案件を獲得して売り逃げないとどんどん魅力がなくなる罠

>>222 サーバは動く金額が大きいから先回りして動かないと市場とれないんだよね。

ていうかそこまでamdが憎いんかな?

>>224 出る前から商業的敗北が確定してる製品に前向きなコメントなんてやりようがないでしょ

いや今の時点で敗北確定がわかるとか未来わかるんですね…

団子がいると冷静な話が出来なくなるから嫌なんだよね

AMDが自社製品よりスペックが劣ると主張してる後発製品が、死ぬほど取りたがってたスパコン案件はもちろんのことクラウド最大手に大口採用が続々決まってたら、その主張はもはや負け犬の遠吠えでしょう。

つーか逆にスパコン以外で何の役に立つのよInfinityFabricなんて

国のトップスパコンは今はそこまでおいしいもんでもなくなった

>>232 クラウドでも中小規模のホスティングメインのとこはプロプラのファブリックどころかInfiniBandすら使わんのが普通よ

ぶっちゃけそういう規模ならXeon Dクラスの省電力・高密度サーバでいいね

インテルスレ、全然盛り上がらないねぇ

こういうネタが理解できるおっさんしか支持層いないんじゃそりゃ自作PCは廃れるわ

真面目に知らんが、今の若者はAMDにもMacにも興味はない

普通に勉強会やハッカソンなどのイベント参加してる大学生のPCの9割がたMacだ

そら深夜アニメを大量に保存してサーバルちゃんがどうだの言ってるのがPCユーザーのメインストリームだと言われても困りますし

>>238 >>243 >>246 >>232 もお前かぁそうかぁ >>247 Intelの次世代で語ることねーからってAMD引き合いに出さなくても良いのよ?

>>242 >>243 >>244 ならなんでAMDファンボーイズやってんの?

>>254 PCは組み立て流ものという前提がない子たちにとって、演算性能性能が必要になった時の最も有効な解決手段が「速いマシンを組む」じゃなくて「クラウドリソースを活用する」だからその点で既にギャップ生じてる

必死になってintel否定して楽しいのか

AMDが必死になってるデスクトップPCに未来なんてねーよって言ってるだけで、Intelはとっくに事業転換を進めてるけどな

そうだね

だからさー余所をけなすしか語るネタねーなら書き込まねーでスレ落としちまえよ

>>264 >>264 インターネットに接続して利用されている全世界の機器のうち、米グーグルのOS「Android」を搭載する機器の数が増え続けており、 https://news.yahoo.co.jp/byline/kokuboshigenobu/20170313-00068639/ >>259 図書券じゃねえ、図書館な

IntelはARMと戦って負けいつか彼らに勝つための経験を得たがAMDは逃げただけだ

>>269 祝。クロミウムのAPNG対応。外圧かかってMSも対応しねーかな。

逆神の法則がついにMacとAndroidにも降りかかるのか

>>273 まあ年配の教員なら使ってる人が多いかなとは思うけど

>>273 (色々なケースを見るけど、いずれにせよ不毛な議論にしかならん気がする)

拗らせた挙句、いよいよ板違いの存在になってしまったか。

機械翻訳がネイティヴ32コアだとか嘘ついてたがハリボテのゴミだからそれなしね

つーかいまどきの大学生が自作デスクトップが趣味かどうかからうまくMacつかってるかどうかに逸らしたつもりだろうけど結局若年者支持層が皆無なんだね

Naplesはそんなでもないけど、Skylake-EPは出たら早く触ってみたいな

IoTセミナーやったとき、大学生や若手エンジニアの9割(某旧帝大含む)がMacBook, おっさん勢にちらほらWindowsつかいがいたけどさすがに自作PC持ってくるやつはいなかったよ

コンテンツクリエイターが何を選ぶかが大事でPC利用者の立場なんてどうでもいいんだわ。

見て来たから言ってるんだよ

そう思ってるならこんな所から出てMac板にでも行けば?

アム厨以外は誰も自作がメインとは言ってないし

勝手にレッテル張って勝手に勝利宣言してるだけだから

エホバと話しても一向に噛み合わないのと同じ

Web業界における「IEじゃないと動かない」はちょっと前まではPCがクラウド時代においてもWindowsが影響力を持つ象徴的ニュアンスで使われてたが

chromebookやasusのスマホをいくつも持ってるなら

FreeBSDやlinuxでnaplesを使う動画配信サービスの話を聞いた。

単純にUbuntuとのデュアルブートにしたいだけだよ

AMD vs Intelを必死にMS disに誘導するの滑稽すぎw

もしappleがamd採用したらどうやって発狂するのか見て見たい。

>>304 「その時になったらやればいい」ってほんと田舎の村役場クオリティ

そういやlightpeakをボロカスに言ってなかったっけ?

どうやら、Windowsが無くなったら「x86だから売れる」という前提すらなくなることがわかってないようだしね

>>310 >>311 IntelはChromebookもトップシェアを維持してるだろ?

中長期的にAndroidといずれに統合してくならARMに寄っていくんじゃないの?

その時には独禁法対策でAMDを生かす価値も無くなってるだろうね。

そうかそうか

あ、そう言えば聞いとくけど

>>318 >>319 AMDを褒めちぎりたいならTwitterの鍵垢作って好きなだけどうぞ

自作と関係ないんでお前がTwitterの鍵垢作って存分に叫んでろ

次のSkylake-XやらXEONやらについての話でも有ったのかと思ったら、また団子のスレチ話かよ…

俺はさ、まともな話を聞きたいのよ。AMDを褒めちぎりたい訳では無いの。

今はちょうど端境期か

GeminilakeはGoldmontの10nmシュリンク?

AMD次世代スレ荒らしまくってたのにここに逃げてきて妄想垂れ流してる糞団子w

>>993 >>475-478 )JRが南海の新大阪乗り入れを認める提案を言い出したから。>>725 にも書いてある >>328 >>331 よくら見たら>>331 って糞団子の自己紹介だよね? おお、つまり君はAMDファンボーイズ版団子なんだね、すごーい!

ご覧の通り苦しくなると逃げるか話題そらしてごまかそうとするゴミクズ基地外糞団子www

>>339 Starshipが7nmで来年とか言ってたアホにブーメラン

RYZEN最上位が3万とか言ってたゴミクズ基地外糞団子は特大ブーメランですが?www

サーバ向けで十分な検証が必要なStarshipが来年出るとは思わないが、

相応にコストかけられる製品でないと釣り合わないんじゃないかな

GbEコントローラすらなくて結局実用上ASMedia製チップが必要なレベルで統合とか言われましても

U/Y系プロセッサだと実装面積とかのメリットあるだろうなとは思うけど、デスクトップだとどうだろ

Skylakeで本当のSoC化な噂があったけど結局AVX512だけのアーキテクチャが出てきただけだった

eDRAMを止めて、FPGAとHBM3を統合する話も無かった?

やはりRYZEN 7-1800X(TDP95W)よりもi7-7700K(TDP91W)の方がゲーム中の消費電力高いじゃんw >>353 それぞれのダイを小さくした上でTSVで2段重ねにするほうが総合的にはお得という主張なのか……

>>359 googleは自分たちの使い方にぴったりなのがその構成なのかねえ。

L1キャッシュ=SRAM

>>364 キャッシュ構造の多段化は、遅延も大きくなるし、設計も複雑になるからコストも膨らむし、その割には大きな性能アップは期待できないなんてことになるから、いいとはいいきれない

次世代RAMが(x86で)実用段階になったら

>>367 「マルチコア化を進めるが、シングルスレッド性能は決して手を抜かない。ベクタ幅は大きくしていく。メモリ階層構造は改善が必要」

むしろ実現するのは Intel 出会ってここで議論するものでもないきg…おやこんな時間に誰だろう

Intelの特許資料の図がミスリード仕様なのは今にかぎったことじゃないし

ふつうPassmarkスコアってマルチスレッドのはず

>>362 >>361 Fig19のことじゃねーの?

>>375 大雑把には似たようなものとも言えるだろうけど、GoogleがSkylake XeonでAVX512使えるって言ってる Intelはここ最近ずっとサーバ用チップを専用設計してきたし、さすがに今回もそうなんじゃないかなあ

>>367 >>380 Omni Path自体はもうカードもスイッチも売ってるし、Oakforest-PACSみたいなHPCでの利用例もある

名前はともかく中身は大丈夫そう。

Skylake Xeonは、コア数&TDP上がってるけど、ちゃんとベースやシングルTBも上がって、 >>370 の方針で実現できてるってことになるか。 Core x2 + PhiAtom x8 でIACellの完成!

>>384 >>377 >>386 みたいなCellのようなCPUになると >>387 400W投入したら28Cでもi7-7700無印に近いくらい回りそう。ダイが大きいから冷却もなんとか IntelのDCでも鉱物油冷却は試みられてるらしい

IBMとかは水冷とかあった気がするけど、Xeonは特殊な冷却できるだけ不要な範囲にTDP抑えて

データセンター全体での消費電力削減の取り組みの一環と言われるかな >液冷とか油冷とか

>>390 富士通M-780(1986年)、NEC SX-2(1985年)、S2000(1987年)

ダウンサイジング、CMOSマイクロプロセッサの台頭で液冷は一旦注目度が

Omni-Path経由でNVLinkパケットを中継してGPUのノード間通信とかなかなかアツがムネい構成

>>393 構内にカビが生えるほど放置されてた天河1号が今では稼働率トップクラスのスパコンに

冷却ならOakforest-PACSはかなり良いのでは

ちなみに京で水冷してるのはCPUとネットワークコントローラのみで筐体全体は空冷だから

>>406 ジサカー「KabyLakeの水冷PCできたで〜」

うろ覚えだけど、富士通は空冷と液冷のハイブリッドと言っていたような

>>401 俺は空冷設備見たことあるからそれの印象で言っただけで

俺のレスちゃんと読み直してくれよ

見てないから何も言ってない

バカがなまじ自作PCの知識で知りもしない巨大コンピュータを語るとこういう齟齬が生じる

Cellの構想自体は間違って居なかったわけだ

Phi統合の次はIA64の機能も完全に吸収してもらいたいね

CELL REGZA、Cellブレード、PS3も出荷終了であと現役のCellはPS Nowだけになる。IA64とどちらが最後まできのこるか?まさかのKittson出荷でIntelが一歩リードか

勝った負けたなら負けで良いよ

>390 ,,・´∀`・,,)っ-○○○ (アウアウウー Sa37-CJUg) sage 2017/03/22(水) 22:25:31.67 ID:lBTmCvhFa >>390 >>393 >>419 >>424 発した熱は屋外に出さなきゃならんのよ

スパコンはよくわからないけどさ

はいはいw

それとも

海や大きな川の沿岸に作ってるのに空冷塔が必要な発電所はないだろ?

>431 ,,・´∀`・,,)っ-○○○ (アウアウカー Sa1b-1VOV) sage 2017/03/23(木) 20:49:40.85 ID:0VH8ZIxwa

ワッチョイついてないスレならIDコロコロ変えて暴れてたところだろうがあいにくだったな

少なくとも自分の知見をもって予測が外れたんだから

京の見学は行ってみたいな

IIJの松江DCPも行ってみるといいよ

>>435 物わかりが悪いな

パソコンのスケールで表すなら京の水冷部分はせいぜいCPUヒートシンク程度の役割だ

もう素人にすら後出しジャンケンの詭弁って見られてるんだから

乗用車のラジエーターも広義の空冷だよ

水冷と空冷が相反する概念だと思い込んでるからバカはバカな発言を続けるわけ

またトヨタの知り合いっていうフカシか

ラジエーターが突き詰めれば空冷だということは誰でも知ってる事だぞ?

誤りを認めると死んじゃう難病だからね

>>449 知恵遅れのオレオレ解釈なんて聞きたくないよ

>>456 >>456 お前の解釈が当該分野で間違ってるって発想がないのね

>>456 WiMAX2+って知ってる?

一応440Mbps対応地域だから無理してひかりの工事する必要もないし

スパコン「京」で復活した「忘れかけられた技術」 スパコンは再び「水冷」へ

「1980年代の大型コンピュータは全て水冷だった」(富士通アドバンストテクノロジHPC適用推進統括部統括部長の鈴木正博氏)

冷却はフィンに対して空気を当てる空冷でも実現できるが、フィンを設置するのに必要となるスペースが水冷とは大きく異なる。例えば、同じ冷却性能を実現することを考えた場合、空冷フィンに必要となるスペースは、水冷のクーリングプレートの10倍となってしまうのだ。

おまえらいい加減考えを改めた方がいいよ

ID変え自演放題のスレなら「ら」になるだろうけど2,3人頭のおかしいのが張り付いてるだけですからね現実問題

乗用車のラジエーターも広義の空冷だよ

AMDスレからわざわざ遠征してCPUの話を一言もできない基地外さんがなに?

Skylake-Xeonはvfmadd*psのレイテンシ6くらいある気がするけど気のせい?

間違えましたごめんなさい

>390 ,,・´∀`・,,)っ-○○○ (アウアウウー Sa37-CJUg) sage 2017/03/22(水) 22:25:31.67 ID:lBTmCvhFa

此の期に及んで空冷では無いなんて素人じみた主張はさすがに恥ずかしいぞ

富士通いわく京は空冷、水冷併用冷却システムだってさ

基地外ゴミクズ糞団子さんすいません、RYZENの1800Xが3万になるのいつですか?

PCでは水枕載せないような低速なモジュール・デバイスでもシステム全体としては熱源になるからラックファン回して空気を入れ替えてるんだよね

それは水冷じゃない、自然界の水、氷、大地などに放熱しないものは「空冷」!

>>482 京では空冷のための設備にもコストをかけてるよねーというだけの話なのに、

まともな人は相手にしないけどフカシたりするから

海水で冷やしてそのまま海に流しても

>>484 空冷以外に使ってるのあればそれが当てはまるのは常識だろ?

自作PCの常識がなぜHPCやエンプラに適用できると思った?

>>485 みんな間違ってるなCPUの熱を

話の枠組みをしっかり定義しないと普通は一般論で解釈されるわな

>>494 おまいらに問題

447 ,,・´∀`・,,)っ-○○○ (アウアウウー Sa3f-1VOV) sage 2017/03/23(木) 21:43:03.70 ID:o/dbU/paa >>447 PentiumMをベースにNetBurstの機能を追加してCoreシリーズを作ったように

フロントエンドは、トランスメタのモーフィング使ったデコーダ、バックエンドをVLIWにすればいいかな。

P4の要素って400MHzのFSBとSSE2サポートくらいだがな(それすら実装方法が大きく異なる)

冷却工程に水使うものが全て水冷だという主張が正しいなら空冷式の発電所なんて存在しないよ

完全ゼロベースのフルスクラッチCPUに、Windowsのせてx86エミュレータ載せたもの作ったほうがいいと思うの

いまだCrusoeの亡霊を見続けてる?

そしてWindowsが電力効率悪い

>>508 Qualcommのあれがそんなにいい様には見えないけどね

いやまあ自分は68kエミュレータやRosetta世代だからの

mipsなのにx86,armのcpuが在るじゃないかw

x86が他を潰して残ったのはスムースな互換性のお陰なのに

>>513 >>514 わかったから、団子の定義の水冷のスパコンを教えてくれ

IntelはIA64で脱x86を失敗したからな、当分x86を存続させるしかない

読解力ねーのか?バカなのか?

>435 ,,・´∀`・,,)っ-○○○ (アウアウカー Sa1b-1VOV) sage 2017/03/23(木) 20:54:40.25 ID:0VH8ZIxwa

米海軍の原子力潜水艦は京の建物よりはるかに小さいけど?

なんで話が発電所になるんだよ

京の冷却の話をしてたのになぜかパソコンの水冷の概念を持ち出したばかのせいですよ

>>524 京は空冷塔相当の冷却設備があるからそう書いたんだが。

お前が京をDCとしてとらえてるからいかんのじゃないの

相手もDCといってる

醜態って

河川や海の水で熱交換してるデータセンターももちろんあるよ

それは議論の枠組みを決めてから言わないと誤解を生じると思うんだけど

>435 ,,・´∀`・,,)っ-○○○ (アウアウカー Sa1b-1VOV) sage 2017/03/23(木) 20:54:40.25 ID:0VH8ZIxwa

>>519 空冷、水冷なんて用語が「便宜上」どう使われているかだろ

「XeonはTDP高いけど冷却はし易いかもね」

AMDのスレで散々Intelの方ガーnVIDIAの方ガーって暴れてたのに

初めてCPUを付け替えるんだけど

各自世代スレは団子をいじり倒すスレになりました。合掌

>>535 >>539 >>539 乗用車のエンジン冷却用ラジエーターを空気で冷やしてるから広義の空冷って言い切っちゃったからな

>>539 Supermicroの8U SuperBlade。205W Skylake Xeonを40個(2wayx20 or 4way x 10)積めるらしい。5個/1Uの密度。 http://prw.kyodonews.jp/opn/release/201703019386/ https://hardforum.com/threads/intel-xeon-gold-xeon-platinum-skylake-sp-lineup-leaked.1928015/ x86-64ベースにIA64の機能を取り込む形がベター

x86-64にIA64と同レベルのレジスタや命令セットを追加拡張したらx86-64の弱点も

ここ20年の知見としては、VLIW自体が、

ia64はむしろあのレジスタ構成自体が弱点なんだが

> L1のヒット率があまりに悪すぎてL2までI/D分離型

あの頃はRISCやVLIWがこんぴゅうたの未来だとまだ言われてた時だから

今はバス帯域を抑えられるコンパクトな命令セットが良いの?

Xtensaは16ビット/24ビットの可変長命令セットだが、64ビット境界(ないし128ビット境界)に合うようにパックする必要がある。そして命令の並び方に制約があるのでデコーダを簡素化しやすい。VLIWの利点を組み込みプロセッサとしてうまく消化した例だな。

とりあえずIA64の整数レジスタ128本はどう考えてもやりすぎでしょ

京 冷却 でぐぐる先生に教えてもらえばあっさり開発責任者の説明が出てくる話なんだが。

一部でも水冷なら空冷じゃないなんて恥ずかしい理論展開したアホの自戒ですか?

レジスタが多いのはよく分からんな……ああ、コンパイラに明示的に使わせるためか?

水冷式エンジンを屁理屈こねて空冷エンジンと言い切った人よりマシかと

レジスタ多くしまくるとコンテクストスイッチで死ねる

>>562 そらコンパイラで静的最適化する前提のインオーダなマシンはレジスタ多くなきゃダメでしょ

依存関係分析の結果、バンドルがnopだらけとか

インオーダ最大2命令実行のCortex-A53でもうまく使えるように、ってことになると32本程度なんじゃね?

>>556 Intelがマイルストーンと自負するPentium Proは早くとも2020年、と

逆に団子の定義で水冷にあたるスパコンの例をあげてくれよ

既に学識者の見解では京も「空冷」に過ぎんのだよ

最近設計されたはずのRISC-Vでも

>>573 >>574 >>515 しかしそう考えると最近のMS、Intelの動きはハードウェア固定化による

空冷で構わんから学識者の名前出してくれる?

x86のレガシー部分を今後捨てていく展開があるとしたら、

LLVMとかJAVAVMをハード実装するイメージか

ここでもフルボッコの基地外ゴミクズ糞団子

>>575 >>580 >>583 >>539 >>583 AMDの方式だとGPU間通信に異なるPCIeコントローラ同士の通信となり、必然的にMCMの配線またぐからそこがネックになるんですけど…

>>587 967 :,,・´∀`・,,)っ-○○○:2015/06/11(木) 07:47:28.46 ID:Gz5QMTnK >>964 >>589 いや、メインメモリの話なんてしてなかったぞ

>>591 別スレでも書いたが

HBMのコストが落ちる前にGPU用途でコストパフォーマンスに優れるとみられるGDDR6が立ち上がる予定だからフェードアウトorRambus独自メモリなみのニッチソリューションの線もありかな

Skylake-XeonでL3容量削減した謎の答えは殻の内側にあるのでは、とみてるのだけど

>>594 Tesla PもHBM2だけじゃ間に合わなかったようで結局GDDR5X版と併売という状況だしな

昨年のHotchipsのあとだけど

自動車で空冷と言ったらかなり範囲が狭くなって

そもそもeDRAMってXeon向けに使うべきだろうと思ってましたわ

Skylake世代からはeDRAMはL4キャッシュではなくバッファメモリ扱いになってる

基地外ゴミクズ糞団子は毎日顔真っ赤にしてホラ吹きまくってますねw

>>599 >>599 >>596 ま、1枚100万するTesla P最上位だけしか載らない程度に消費者向けとして売るには生産キャパも歩留まり率も追いついてないといえるかもね

コスト的な理由で、当分メインメモリはDDR系じゃないかなあ

Cannonlakeだが、2コア+GT2だとシュリンク率的に1cm角を大幅に割り込むからトランジスタバジェットを何かしらで埋める必要があって、かつメモリ帯域も緩和するためのバッファが必要になる

でもロジックプロセスでDRAM作るのは効率悪いし、もうスタックドメモリが見えてきてる(>_<)

でもIntelがまさかのeDRAMだった

>>613 でもHBMがシリコンインタポーザを除去できるようになり次第eDRAMからHBMに

>>611 >>605 空冷がなくなったの20年近く前みたいだね >>617 >>612 >>609 ,,・´∀`・,,)っ-○○○ (アウアウウー Sa3f-1VOV)

>>620 私はscまでカキコしてるぞ

HBM、HMCは接続、パッケージの分類だから並ぶのはDDRx、XDRなど

モバイル系ノートだとCPUとeDRAM、PCHが1つのモジュールに乗ったのが

ハイファはIBMと違ってeDRAMを外に出したけど(VRと一緒にw)、PCHとeDRAMのダイ統合に夢を見てる

じっさい16GBでほぼ打ち止めが見えてきた一般用途だと

intelは耐用年数を下げるためにSSDをダイにのっけ始める

未だに22nmでeDRAM作ってるのは稼働率低迷で22nmの減価償却期間を伸ばさざるを得なくなったからと把握してる

More Mooreと言われている三次元積層がもし順調に進むのなら、

積層ぶんだけコスト増すに決まってる

まあ、メモリ版の三次元積層がHBMとかHMCと考えてみればイメージできるだろ

L4キャッシュとビデオメモリーはHBMに

eDRAMも8層化くらいすれば1GB程度の容量と1TB/s程度の帯域は確保できるかもね。ロジックプロセスで作るからオンダイ化もできる

eDRAM多層化とか馬鹿みたいなことは言わない方がいいぞ

逆に何か問題でも?

マルチレイヤーってTSVによる3次元積層の話でしょ

だからそれは単なる積層で同一ダイに作り込むオンダイじゃないでしょ

>>644 それは正確ではないな

メモリ帯域が飽和してコアが処理待ちで待機状態になればたしかに最大消費電力は抑えられるかもしれないが待機してるぶんだけ無駄飯食ってるだけだ

実ゲームで7870Kの倍以上のフレームレート叩き出してりゃ十分消費電力以上の仕事してるってみなしていいのでは?

学生さんか研究者か知らんけど大学だか学校の回線から2chなんかに書き込んで

QualcommのDragonBoardなんて安いスマホ用のSnapdragon410のSoCそのまんま使い回しだし、垂直統合目指す会社でIoT専用の製品ライン用意できてるの現状Intelくらいなのでは。

顧客のニーズに合わせた製品を供給できるということ

Iotとかどうせ失敗する

IntelのIoT部門単独でAMDの組み込み・カスタム部門(ゲーム市場向けがこれに含まれる)以上の売り上げ・利益叩き出してるんだけどな

負けることにしないとIoT向けで何も弾がないAMDの一人負けが確定してしまうからファンボーイ発狂モノである

数だけならIntel以上のチップを生産してるワンチップマイコンの老舗は多数あるがインターネット・セキュリティの実装が完備してるものは皆無に近いのね

次の目標はCoreクラスのパフォーマンスでTDP2W台のSoC。CPUはメニーコア対応、もしくはGPGPU超強化でPhi(とIA64)も取り込む形で

HBMはけちょんけちょんに貶すくせにeDRAMの積層化はアリとする二重基準・・

そもそもIntelのIoT部門はIoTがIoTと呼ばれる前(ユビキタス〜とかスマート〜)からやってて利益上げてる分野を独立部門に格上げしただけで、スマホのようなレッドオーシャンにx86市場をいきなり立てようとしたわけではないのよ

eDRAMって64MBだろ?

アホが64MBより小さいキャッシュはいらんと言ってますよ!

まるで永年の知り合いのように、Intelの気持や癖をあざやかに忖度するコテ (「秋津温泉」改変)

なぜわざわざ密度の低いeDRAMを使うのか

IoTという言葉が流行る前段階でネットワーク構築、データ収集、マネタイズに至るまでの全てのノウハウを既に確立してる。

HBM(のようなもの)、

>>640 >>672 まさかIntel入ってるデジタルサイネージ自販機の発出がいつなのかも知らないの?ニートのクズなの?

ま、AMDがPCが儲からなくなってからIoTを始めようと思ったところで

そういえばATMの殆どがWindows XPで動いていて切り替えが終わるのは2019年ごろとか言われてたからまだXPのATMは現役のはず

いまだに謎なんだがIntelってなんでPGAからLGAソケットに変えたんだ?

>>679 接合箇所が増えるからじゃ

検索するとLGAの方が寄生インダクタンスが小さいという情報があるな

成り立っていることだとしても

コストでしょ

L1キャッシュ=SRAM(32KB)

STT MRAMでHBMより上位のキャッシュ狙えるならHBMなんていらんだろ

何気に22nm HP/LLは初出な気がする

オリジナルの14nmと14++で性能が違いすぎるな

>>689 Skylake-XeonはL2 1MBになったよ。

kwskって自分でスライド見てくれよ 簡単にいうと、モジュラー化したダイを広帯域程消費電力のEMIBで繋いでカスタム製品を迅速に投入できるわけよ

>>697 たぶんこれは製造から見た視点であって製品発売じゃないから、時期が早いこと自体はおかしくないかと

Intelは相変わらずプロセス面は優秀だな

断面画像が綺麗で感心するが、チャンピオンを持って来てるだけなのかな

>>701 >>697 RPi Zero W発売中止(国内使用不可)はさすがに草不可避ですわ

Intel以外で製造のダイがEMIBで貼り合わせられるのかどうかは書いてない気がする?

Arria10はTSMC20nmだよ。

あと、Mark Bohrの資料に、何気に見たことのない

>>697 ただKabyLakeになるとモバイル向けの省電力処理チューニングが進んで

Kabylake自体U/Y先行だったしデスクトップがおまけなのは当たり前

14nm+はSkylake Xeonが一番重要かな。コア数拡大やAVX512をできるだけ高いクロックで回して性能上

>>623 LGAで低コストになるならAMDだってLGAにしてると思うよ

AMDはHEDT向けの12C、16CのRyzen用ソケットはLGAにするようだな

Skylake-Wは10コア6コア4コアで全て140W >>714 >>718 >>640 投資場(敢えて誤字)はFlashAirとかいろいろ可能性感じるのだけどね

まぁモデム作れないインテルは結局本命じゃないんですけどね

日本においてはWiMAXはものすごく成功してたんだけどなあ

最後の1マイルだっけ?

うちのWiMAX2+ルータ、220Mbps対応のやつで5Mbpsしか出なかったものが440Mbps対応の最新機種にしただけで実効40Mbps普通に出るようになって軽く困惑したな

2+はau回線のiPhoneもUQ WiMAX2+のキャリアアグリゲーション対応してて

youtubeの144pが200kbpsでもみれるのでわりと速度はどうでもいい

ocn moble oneの制限速度が200kbps

>>690 >>695 >>722 鳴り物入りの3D-xpointがショボいHDD cacheに成り下がってるが

3D Xpointは最近のIntelのやらかしで一番酷い

カタログスペックでDWPDが30ってエンタープライズ向けSSDでもそうそうないぐらい大きいから、初期製品としては相当いい方だと思うけどなあ http://www.anandtech.com/show/11208/intel-introduces-optane-ssd-dc-p4800x-with-3d-xpoint-memory >>737 ようやく読み書き35ns未満を実現とか言ってる時点でx86クラスのCPUのL2には遅すぎまふ

>>743 HBMやHMCの中のメモリーは現在はDDR4?で将来はDDR5に?

>>746 >>747 東芝の半導体が売りに出てるけど、Intelは手を出すまでもないって感じなのかな?

>>752 フラッシュメモリの工場だしIntelは買わんでしょ

これから原子力産業に参入するとかよっぽど考えがないとね。

>>741 >>752 >>750 HBMやHMCで使われているメモリーはDDRとは別物なのですね。

メモリーがどこまでを指すかだけど、

DRAMが素子名でDDRとかHBMとかHMCはチップの内と外でやり取りする際の電気的特性を規格化したもの

下手に熱源に近づけるとDRAMが高温で特性悪化しちゃうらしいのと

EMIBは一見スマートな技術に思えるけど、細かい点を突き詰めると結構めんどそうなんだよな

EMIBはあくまで高密度なバンプを扱えるようにするだけで

>>765 >>770 1兆回で劣化がなく300℃で10年保持のNanotubeRAM

RYZEN今回のwinアプデ結構いい感じで最適化入ってるらしい。どんだけ変わるか楽しみだ。

RyzenはGTX1080Ti刺してCUDAという目的で安定して動かないらしいからなぁ

>>771 ネタだけど、

インテルもさっさとAMDみたいにサウスブリッジ完全統合して欲しいね

5nm世代以降になると思うけど

>>778 Coffee Lakeも実は4コアだったってオチが残ってたりしてw

>>778 >>778 >>778 >>782 >>772 Intel’s X299 HEDT Platform with LGA 2066 Socket Codenamed ‘Basin Falls’ http://wccftech.com/intel-basin-falls-x299-hedt-platform/ ryzenに対抗して急遽12コアモデルを投入するって話があったけど結局ガセだったのね

>>784 統合してるからなんのメリットがあるのか?

統合したら安いんだろ、全部一々開発せずに済むし

(実態が2ch×4だろうが)メモリ8chで4000ピン超えの巨大ソケットの時点でマザボが高コストになるし結局IOハブが別途必要だからコストダウンになってないぞ

安くなった分で補えるんじゃねーの……

Skylake-EPだと3647ピンらしいしあんまり変わらんだろうな

Naplesのチップセット要らないという部分、解説する人によって解釈が違うんだよね

>>793 AVX512だってIntelもXeon系が対応している事はしているが256bitを2回回しての対応でしょ

面白い仮説だな

64SP / 32 DP Flops/Cycleと言ってるから512bit FMAx2じゃないと不可能

>>784 何れにしてもeDRAMかMCDRAM載せないと帯域間に合わん

>>801 GoogleのAI開発を支えるディープラーニング専用プロセッサ「TPU」 http://news.mynavi.jp/articles/2017/04/11/tpu/ >intelのcpuが同時に何か行うこと

そこそこの仕事を複数同時に行う上でのコスパがRYZENは競合に対して高いと書いてあるな

>>776 >>803 >>811 >>812 最近のIntelは、コンピューティングの改善のためなら

やはりAMDががんばるとIntelもがんばって面白いな

AMDあんまり関係なくて、具体的な採用先、例えばApple辺りがつついたんじゃないかなあ

現状4GBをHBM2で繋げられるってことは、もう少し頑張れば8GBやれるってことで

その4GBや8GBは、GPUに付いてるビデオメモリだから、CPU側から使えないよw

IntelがeDRAMと内臓GPUを捨てるとはねぇ

メインメモリ帯域よりはるかに狭いPCIe x8接続だからVRAMをL4キャッシュとして使うのも非現実的だぞ

>>810 流石にこれからeDRAMが日の目を見ることはないだろw

>>817 リンゴの採用するRadeonは何かと特殊仕様が多いからな

なんにせよ面白いね

本来のロードマップがどうなのかは気になるところではある

ドル箱の機械学習はカスタムやFPGAに太刀打ちできないし

>>828 >>825 つまり、RavenRidge発売後にIntelへのGPU供給をやめればIntelはPC向けは全滅するということかな

>>832 いや、PC向け売れないと売り上げ大幅減で開発もままなくなるだろ

Kabylake-Gに関しては、少なくとも現時点では特殊な製品としか言えないんじゃないかなあ

微妙に食い合わない

別に互いにつぶしあうのが目的でなくて長期的に儲かればいいわけだしな

手抜きには呆れてたけどボッタかと言われるとそうでもない

>>832 >>839 ボッタもそうだけど品薄でメーカーにも供給出来なくて自滅してたな

>>840 >>840 >>842 あんた久しぶりだな

とわ言え、Ryzen と Sandy Bridge の演算性能は似たようなものす。 IntelがDCvs.PS2のときみたいな戦略できてるな

ところで

>>840 >>848 >>849 CPUキャッシュについてのIntelの方針はよくわからんけど、

そもそもの話、MBPでもeDRAM載ってたのはdGPUレスのモデル限定ではないし、CPUの帯域拡張目的でも一定の成果が出ていたはずだ

>>852 別ダイで作るならDRAMに比べて密度の低いeDRAMを使う意味がないことくらい理解できそうなものだが

>>854 eDRAMはリテンションタイムの問題があるからプロセスが変わったら基本的に全部再設計が必要

>>855 CPUは互角、iGPUと高性能メモリーはAMD依存になっていきそうだけど、そうすると今後のIntelってどうやって競争していくんだろう

>>858 >それに、やる気があればSkylake-XにeDRAMを使えたはずだけどやってない

>>859 >>862 RDRAMから始まるIntelのメモリへのアプローチでeDRAMはとても奇異ながらもIntelの現状に合致しそうなソリューションだった。

>>859 >>864 Intel自身がeDRAMの失敗認めてるしなぁ

eDRAMなしでIrisついてたのもあるし、ブランドはあまり関係なくなってた気がする。実質的にはGT3以上?

>>840 メインメモリーはDDR5の後継として将来HMCになるかも知れないが

そもそもeDRAMの売りは混載出来る事なのになんで別チップになってんの

メインが14nmに移行して22nmに余裕ができたからじゃない

>>874 記事形式の広告(アルプス電気)だが http://news.mynavi.jp/kikaku/2017/04/14/001/ DRAMと通常制御回路は高さが思いっきり違うから、その高さを

別チップにしないといけないのは分かったけどそれにeDRAMの名を冠した理由がわからないな

>>880 >>880 >>874 うーん、団子他諸氏にききたいけど、 >>874 ワンチップってどーゆー意味で言うてんの?

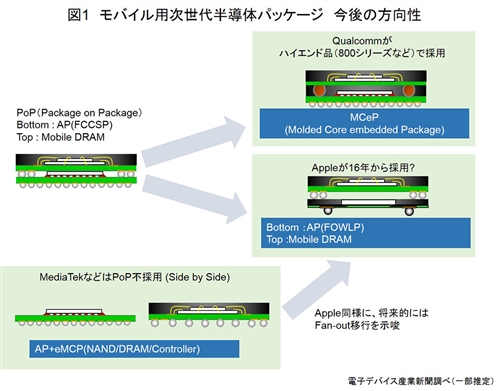

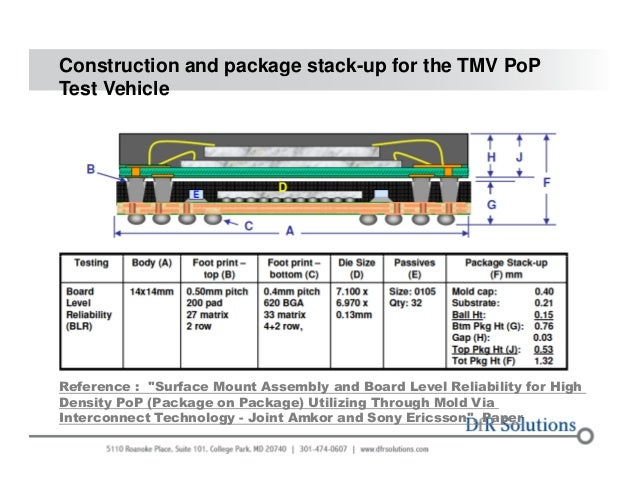

例えばスマホだとPoPって形でメインメモリを重ねた構成は見られるので、

1、2年では無いと思うけど普通にその方向に向かってると思う

PoPならiPhoneは7年前、ガラケーは十数年前からそうなっとるがな

スマフォ向けとかはチップが1Wとかだから積層できるんだが

最近はMCMやSiPでもワンチップって書かれることがままだからな。どこぞがPCHをオンパッケージにしてSoCとか宣ってるのが原因だと思われるが

ID被りとかしょっちゅうあることやがな

>>887-892 >>885 Kabylake-GがHPC向けだとphiは御払箱かな

>>885 >>900 >>899 たぶんMacオタも「愛知県幡豆郡」在住なんじゃねーの?

DRAMとCPUは同じダイにできるが、そういったことができるプロセスは微細化が進んでおらず、

>>803 このスレ見てるとeDRAM終わってしまったものであるかのように錯覚してしまうが >>907 >>901 まあシリコンインターポーザ自体が高コスト要因ですけど

特にメモリ回りのソケット〜DIMM配線やコネクタがなくなれば

メモリやシステムストレージをオンパッケージ化できればな

メモリができるんじゃないかって話なんでは上のEMIBは

>>917 技術寄りの発表は必要に応じて適宜開催になるのかなあ

インテルが上手く行ってないことを印象づける出来事。

>>920 Intelも(というか各社も)イベント自体はやってるので……

>>920 もう大手クラウド事業者だけで売り上げの大半決まるから泡沫の開発者のために高い金かけて定期イベント開くだけ無駄ってことでしょ

>>929-930 ファブ抱えた巨象とファブレスの身軽なネズミの身の振り方を同列に

だってそうでしょ主要ユーザーはスマートフォン使ているんですよ

>>932 IDF終了とか10nm遅延とかRADEON採用とか最近のintelは異変が多いな

14nmからおかしい、Skylakeもとてもハイファの仕事とは思えない

この5年で競合も替わったし、狙うべき市場も変わったのだから、IDFに代わる場が必要となるのは必然

>>933 企業が変わらずに生き残り続けられる分野って技術系にはあまりないんじゃないか

でも、モバイルなATOMは撤退だよね。

まあ割と真面目な話、Alteraの次のハイエンドはIntel 10nm採用でARMとのSoC製品も出るらしいから

>>948 本番は半導体のターゲットも市場的にも低周波数のノート向けとサーバー向けだろうけど。

ノートより遅れて出す号砲にどれだけの意味があるかは知らない。

>>946 >>944 問題はノートの4コアでどの程度のかちがあるかってことなんだよなあ

>>935 ファブ分離はいいアイデアだけど10年前にやっとくべきだったよね

>>953 >>954 >>958 Pentium N4200はマルチスレッド性能はCore Mよりも高い上にターボ時消費電力もCoreMより低いが…

既にARMが広まってるのにスマホ・タブレットでAtomを搭載するメリットあんまなくね?

iPhoneは10マンで売れるがA10は30ドル強で作らせてる

>>963 そして低価格である必要があるので

ARMでできるならARMのが良くない?

もちろん大多数のベンダーにとってARMを選ぶメリットを与えないだけのコスパを提供できてるからないと感じてるからAtomベースのCeleronが一番選ばれてる

ARMでWindowsが動かせないって言うのが一番大きい気がするけどね

Windowsってメリットかねえ?

低価格かどうかを決めてるのはIntelの価格政策であって

x86版Androidの普及頑張ったからこそChromebookでもてっぺん維持できてるんよ?

Atomの新規開発やめたは大嘘

逆にIntelにとってIoTが銭になる理由は、vxworksなどのソフト資産抑えてるし日本含めて大手のSIer囲い込んで上流から大型プロジェクト引っ張ってるから。

U型番が4コアにシフトするのはPCの性能要求が上がってるからというより、むしろデスクトップ使ってた法人客がノートやコンパクトデスクトップに移行してくるからだと考えたほうが正解だと思うよ

WinタブレットはやっぱAtomが良いわ。

儲からないATOM切るのは良いけど

IntelはWintel囲い込みが成功したx86で強かったが

シングルで決定差がつけられずマルチで物理コア差に負ける、さらにApolloLakeで対応してるDDR4にも非対応の残念石に変わりなさそうだけど…

>>979 パソコンで生活や業務の改善考える時代が終わって携帯電話、さらにいままでネットに繋がってなかった「モノ」に移行してる段階。

単価1ドルかそれ未満のマイコンからちまちまマージンとっても儲けになんないしIntelもそこの商売をする気は無い

Windowsもクライアント側含めてARM移行進めてるからな

>>980 Intelの話かと思った

その場しのぎで適当なことをほざくから小バカにされるわけで

>>991 末端のセンサーデバイスにはSnapdragonすら必要とされてないからQualcommは慌ててNXP買収したわけで

少なくともここで重要性を説いたところで

まぁ、その機械学習においては競合他社と比べて別段アドバンテージはないけどな

数を捌く必要が無ければ、

lud20230108143707ca

このスレへの固定リンク: http://5chb.net/r/jisaku/1487768349/ ヒント: 5chスレのurlに

http ://xxxx.5ch

b .net/xxxx のように

b を入れるだけでここでスレ保存、閲覧できます。

TOPへ TOPへ

全掲示板一覧 この掲示板へ 人気スレ |

>50

>100

>200

>300

>500

>1000枚

新着画像 ↓「Intelの次世代CPU/SoCについて語ろう 82©2ch.net YouTube動画>1本 ->画像>28枚 」 を見た人も見ています:・Intelの次世代CPU/SoCについて語ろう 79 Intelの次世代技術について語ろう 91 Intelの次世代技術について語ろう 99 Intelの次世代技術について語ろう 90 Intelの次世代技術について語ろう 97 Intelの次世代技術について語ろう 96 Intelの次世代技術について語ろう 110 Intelの次世代技術について語ろう 89 Intelの次世代技術について語ろう 98 Intelの次世代技術について語ろう 101 Intelの次世代技術について語ろう 116 Intelの次世代技術について語ろう 118 Intelの次世代技術について語ろう 133 Intelの次世代技術について語ろう 100 Intelの次世代技術について語ろう 135 Intelの次世代技術について語ろう 106 Intelの次世代技術について語ろう 93 Intelの次世代技術について語ろう 125 Intelの次世代技術について語ろう 104 Intelの次世代技術について語ろう 109 AMDの次世代APU/CPU/SoCについて語ろう 300世代 AMDの次世代APU/CPU/SoCについて語ろう 266世代 AMDの次世代APU/CPU/SoCについて語ろう 277世代 AMDの次世代APU/CPU/SoCについて語ろう 247世代 AMDの次世代APU/CPU/SoCについて語ろう 290世代 AMDの次世代APU/CPU/SoCについて語ろう 264世代 AMDの次世代APU/CPU/SoCについて語ろう 282世代 AMDの次世代APU/CPU/SoCについて語ろう 237世代 AMDの次世代APU/CPU/SoCについて語ろう 284世代 AMDの次世代APU/CPU/SoCについて語ろう 279世代 AMDの次世代APU/CPU/SoCについて語ろう 294世代 AMDの次世代APU/CPU/SoCについて語ろう 261世代 AMDの次世代APU/CPU/SoCについて語ろう 295世代 AMDの次世代APU/CPU/SoCについて語ろう 303世代 AMDの次世代APU/CPU/SoCについて語ろう 278世代 AMDの次世代APU/CPU/SoCについて語ろう 291世代 AMDの次世代APU/CPU/SoCについて語ろう 246世代 AMDの次世代APU/CPU/SoCについて語ろう 234世代 AMDの次世代APU/CPU/SoCについて語ろう 276世代 AMDの次世代APU/CPU/SoCについて語ろう 313世代 AMDの次世代APU/CPU/SoCについて語ろう 253世代 AMDの次世代APU/CPU/SoCについて語ろう 283世代 AMDの次世代APU/CPU/SoCについて語ろう 254世代 AMDの次世代APU/CPU/SoCについて語ろう 281世代 AMDの次世代APU/CPU/SoCについて語ろう 311世代 AMDの次世代APU/CPU/SoCについて語ろう 285世代 AMDの次世代APU/CPU/SoCについて語ろう 302世代 Intelの次世代技術について語ろう 130 (19) AMDの次世代APU/CPUについて語ろう第107世代 AMDの次世代GPUについて語ろう AMDの次世代技術について語ろう NVIDIAの次世代技術について語ろう AMDの次世代GPUについて語ろう 6世代 AMDの次世代GPUについて語ろう 3世代 AMDの次世代GPUについて語ろう 8世代 AMDの次世代コアについて語ろう 245世代 AMDの次世代APU/CPU/SoCについて翻訳しよう5スレ目 Intelの焼き鳥技術について語ろう (39) 12世代IntelプロセッサーでCPUが歪む不具合発覚 ■ Intel CPUに深刻な欠陥 Core i世代以降が対象 12世代IntelプロセッサーでCPUが歪む不具合発覚 ★2 AMDの次世代プロセッサを応援しよう part3 12世代CoreでAMDの絶対的優位性が崩れIntelが優位に

13:32:08 up 6 days, 14:35, 2 users, load average: 112.38, 125.79, 127.17

in 0.090065956115723 sec

@0.090065956115723@0b7 on 012003